# PARALLEL AND DISTRIBUTED COMPUTING TECHNIQUES IN BIOMEDICAL ENGINEERING

#### **CAO YIQUN**

(B.S., Tsinghua University)

#### A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

AND

**DIVISION OF BIOENGINEERING**

NATIONAL UNIVERSITY OF SINGAPORE

2005

# **Declaration**

The experiments in this thesis constitute work carried out by the candidate unless otherwise stated. The thesis is less than 30,000 words in length, exclusive of tables, figures, bibliography and appendices, and complies with the stipulations set out for the degree of Master of Engineering by the National University of Singapore.

Cao Yiqun

Department of Electrical and Computer Engineering

National University of Singapore 10 Kent Ridge Crescent, Singapore 119260

National University of Singapore

# **Acknowledgments**

I would like to express sincere gratitude to Dr. Le Minh Thinh for his guidance and support. I thank him also for providing me an opportunity to grow as a research student and engineer in the unique research environment he creates.

I have furthermore to thank Dr. Lim Kian Meng for his advice and administrative support and contribution to my study and research.

I am deeply indebted to Prof. Prof. Nhan Phan-Thien whose encouragement as well as technical and non-technical advices have always been an important support for my research. Special thanks to him for helping me through my difficult time of supervisor change.

I would also like to express sincere thanks to Duc Duong-Hong for helping me through many questions regarding biofluid and especially fiber suspensions modelling.

Most importantly, my special thanks to my family and my girlfriend. Without your support, nothing could be achievable.

# **Table of Contents**

| Chapter 1 Introduction1                                           |

|-------------------------------------------------------------------|

| 1.1 Motivation                                                    |

| 1.2 Thesis Contributions                                          |

| 1.3 Thesis Outline                                                |

| Chapter 2 Background10                                            |

| 2.1 Definition: Distributed and Parallel Computing                |

| 2.2 Motivation of Parallel Computing                              |

| 2.3 Theoretical Model of Parallel Computing                       |

| 2.4 Architectural Models of Parallel Computer                     |

| 2.5 Performance Models of Parallel Computing Systems              |

| 2.6 Interconnection Schemes of Parallel Computing Systems         |

| 2.7 Programming Models of Parallel Computing Systems              |

| Chapter 3 Overview of Hardware Platform and Software Environments |

| for Research in Computational Bioengineering34                    |

| 3.1 Hardware Platform34                                           |

| 3.2 Software Environments for Parallel Programming                |

| Chapter 4 Parallel Fiber Suspensions Simulation                   |

| 4.1 An Introduction to the Fiber Suspensions Simulation Problem   |

| National University of Singapore i                                |

| 2 Implementing the Parallel Velocity-Verlet Algorithm using Conventional    |     |

|-----------------------------------------------------------------------------|-----|

| lethod                                                                      | 48  |

| 3 Performance Study of Conventional Implementation                          | 52  |

| 4 Communication Latency and the Number of Processes                         | 55  |

| 5 Implementing the Parallel Fiber Suspensions Simulation with Communication | on  |

| verlap                                                                      | 68  |

| 6 Results                                                                   | 77  |

| 7 Conclusion                                                                | 85  |

| pter 5 Parallel Image Processing for Laser Speckle Images                   | 87  |

| 1 Introduction to Laser Speckle Imaging Technique                           | 87  |

| 2 Previous Work                                                             | 96  |

| 3 Parallelism of mLSI Algorithm                                             | 99  |

| 4 Master-worker Programming Paradigm                                        | 100 |

| 5 Implementation                                                            | 103 |

| 6 Results and Evaluation                                                    | 119 |

| 7 Conclusion                                                                | 127 |

| pter 6 Conclusions and Suggestions for Future Work                          | 129 |

| 1 Conclusions                                                               | 129 |

| 2 Areas for Improvement                                                     | 131 |

| 3 Automated Control Flow Rescheduling                                       | 131 |

| 4 Programming Framework with Communication Overlap                          | 133 |

| 5 Socket-based ACL Implementation                                           | 134 |

|                                                                             |     |

|    | 6.6 MATLAB extension to ACL | . 135 |

|----|-----------------------------|-------|

|    | 6.7 Summary                 | . 136 |

| Bi | ibliography                 | 137   |

## **Abstract**

Biomedical Engineering, usually known as Bioengineering, is among the fastest growing and most promising interdisciplinary fields today. It connects biology, physics, and electrical engineering, for all of which biological and medical phenomena, computation, and data management play critical roles. Computation methods are widely used in the research of bioengineering. Typical applications range from numerical modellings and computer simulations, to image processing and resource management and sharing. The complex nature of biological process determines that the corresponding computation problems usually have a high complexity and require extraordinary computing capability to solve them.

Parallel and Distributed computing techniques have proved to be effective in tackling the problem with high computational complexity in a wide range of domains, including areas of computational bioengineering. Furthermore, recent development of cluster computing has made low-cost supercomputer built from commodity components not only possible but also very powerful. Development of modern distributed computing technologies now allows aggregating and utilizing idle computing capability of loosely-connected computers or even supercomputers. This means employing parallel and distributed computing techniques to support computational bioengineering is not only feasible but also cost-effective.

In this thesis, we introduce our effort to utilize computer cluster for 2 types of computational bioengineering problems, namely intensive numerical simulations of National University of Singapore

fiber suspension modelling, and multiple-frame laser speckle image processing. Focus has been put on identifying the main obstacles of using low-end computer clusters to meet the application requirements, and techniques to overcome these problems. Efforts have also been made to generate easy and reusable application frameworks and guidelines on which similar bioengineering problems can be systematically formulated and solved without loss of performance.

Our experiments and observations have shown that, computer clusters, and specifically those with high-latency interconnection network, have major performance problem in solving the 2 aforementioned types of computational bioengineering problems, and our techniques can effectively solve these problems and make computer cluster successfully satisfy the application requirements. Our work creates a foundation and can be extended to address many other computationally intensive bioengineering problems. Our experience can also help researchers in relevant areas in dealing with similar problems and in developing efficient parallel programs running on computer clusters.

# **List of Figures**

| Figure 2-1 A simplified view of the parallel computing model hierarchy                                    |

|-----------------------------------------------------------------------------------------------------------|

| Figure 2-2 Diagram illustration of shared-memory architecture                                             |

| Figure 2-3 Diagram illustration of distributed memory architecture                                        |

| Figure 2-4 Typical speedup curve                                                                          |

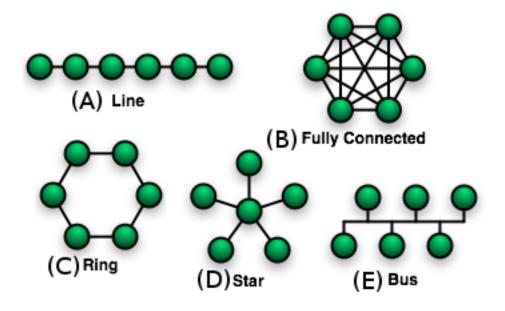

| Figure 2-5 Illustrations of Simple interconnection schemes                                                |

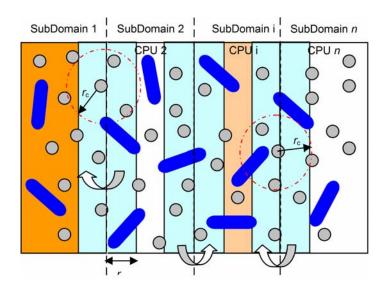

| Figure 4-1 Division of a fluid channel into several subdomains                                            |

| Figure 4-2 Pseudo code of program skeleton of fiber suspensions simulation 50                             |

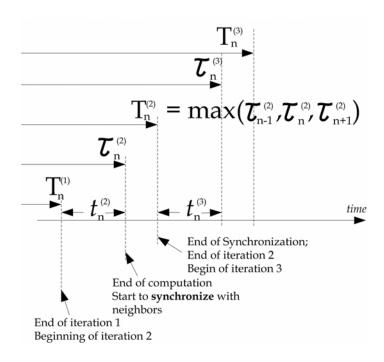

| Figure 4-3 Relationship between time variables defined for execution time analysis 60                     |

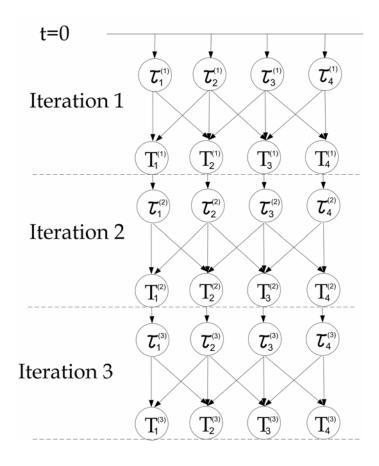

| Figure 4-4 Directed Graph illustrating calculation of execution time                                      |

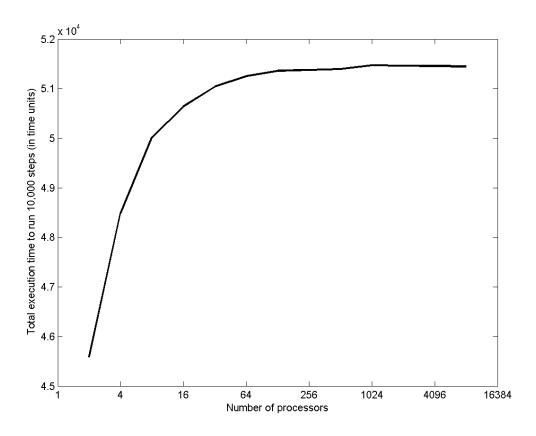

| Figure 4-5 Simulation result: execution time versus number of processes                                   |

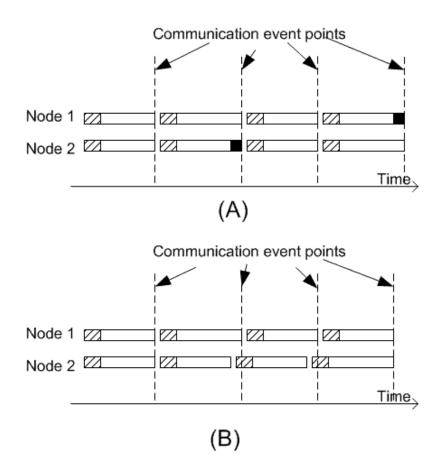

| Figure 4-6 (A) non-overlap versus (B) overlap: comparison of latency                                      |

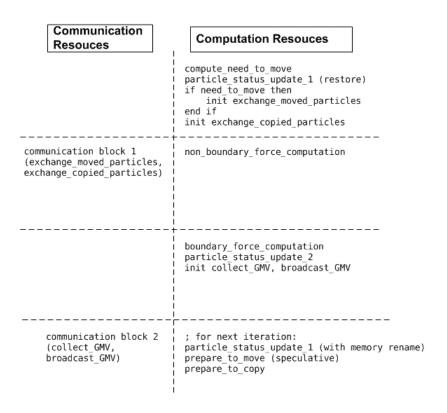

| Figure 4-7 Extended pseudo-code showing the structure of main loop                                        |

| Figure 4-8 Rescheduling result                                                                            |

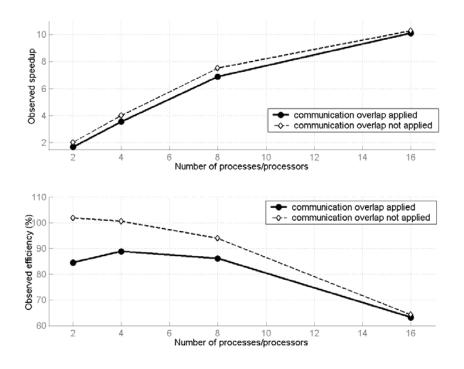

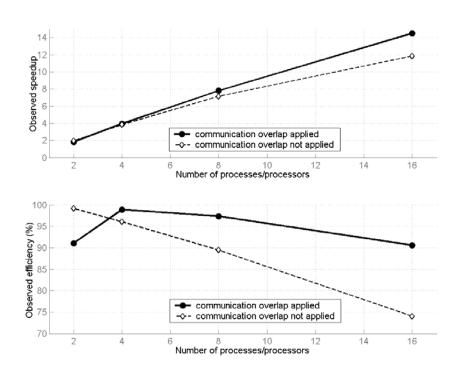

| Figure 4-9 Observed speedup and observed efficiency on zero-load system                                   |

| Figure 4-10 Observed speedup and observed efficiency on non-zero load system 85                           |

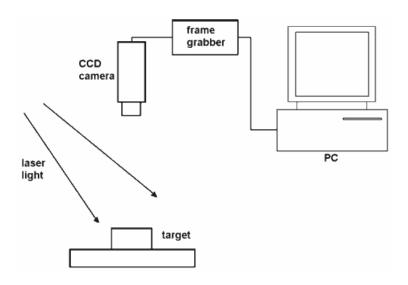

| Figure 5-1 Basic setup of LSI with LASCA                                                                  |

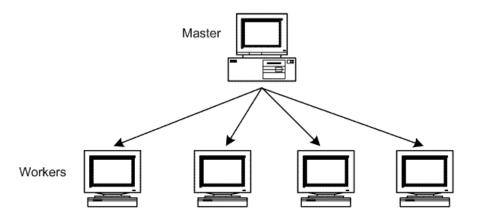

| Figure 5-2 Master-worker paradigm                                                                         |

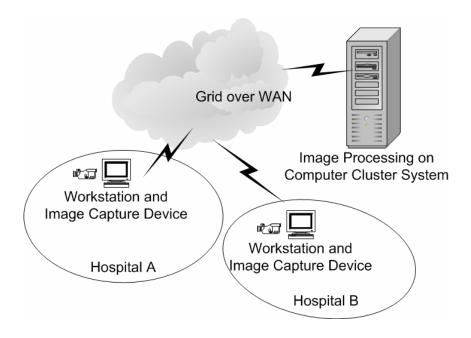

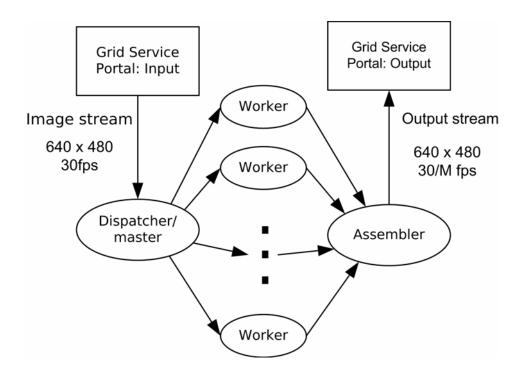

| Figure 5-3 Illustration of top-level system architecture                                                  |

| Figure 5-4 Illustration of master-work structure of speckle image processing system 107                   |

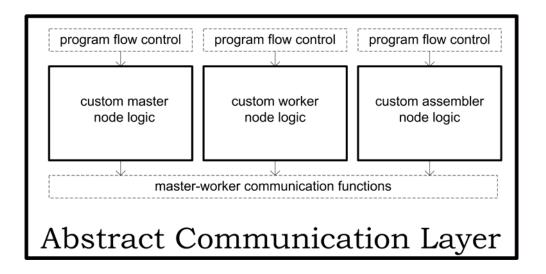

| Figure 5-5 Architecture of Abastract Communication Layer                                                  |

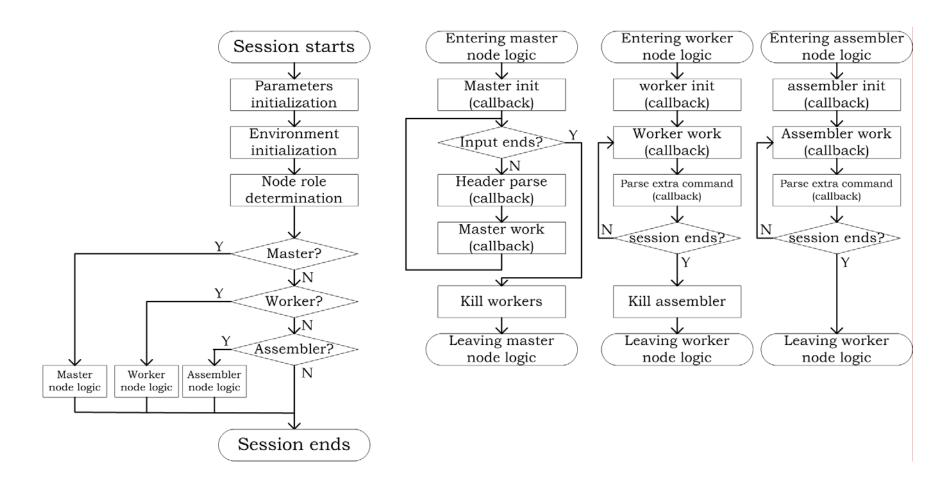

| Figure 5-6 Flowchart of the whole program, master node logic, worker node logic, and assembler node logic |

# **List of Tables**

| Table 4-1 Performance profiling on communication and computation calls                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Table 4-2 CPU times with and without the communication overlap applied77                                                          |

| Table 4-3 Performance evaluation results: zero-load system                                                                        |

| Table 4-4 Performance evaluation results: non-zero load system (original load is 1) 85                                            |

| Table 5-1 Time spent on blocking communication calls under different conditions 121                                               |

| Table 5-2 Time spent on non-blocking communication subroutines with different data package sizes and receiver response delay time |

| Table 5-3 Time spent on non-blocking communication calls under different conditions                                               |

| Table 5-4 Time spent on processing 1 image frame when no compression is used 125                                                  |

| Table 5-5 Comparison of different compression methods                                                                             |

| Table 5-6 Time spent on processing 1 image frame when LZO compression is used . 127                                               |

|                                                                                                                                   |

# **Chapter 1 Introduction**

The domain of this research is effectively utilizing parallel and distributed computing technologies, especially computer clusters, to support computing demands in biomedical research and practice. Two typical computational problems in bioengineering field are numerical simulation, which is very common in research in computational fluid dynamics; and biomedical image processing, which is increasingly playing an essential role in research in diagnostic and clinical experiments. The complexity of biological systems imposes severe requirements on computing power and latency on both types of problems.

Parallel computing promises to be effective and efficient in tackling these computation problems. However, parallel programming is different from and far more complex than conventional serial programming, and building *efficient* parallel programs is not an easy task. Furthermore, the fast evolution of parallel computing implies algorithms to be changed accordingly, and the diversity of parallel computing platforms also requires parallel algorithms and implementations to be written with consideration on underlying hardware platform and software environment for research issues in bioengineering.

In this thesis, we investigate how to effectively use the widely-deployed computer cluster to tackle the computational problems in the aforementioned two types of bioengineering research issues: numerical simulations of fiber suspension modelling, and laser speckle image processing for blood flow monitoring. Computer cluster imposes several challenges in writing efficient parallel programs for those two types of applications, in terms of both coding time and run-time efficiencies. For instance, relatively larger communication latency may hinder the performance of parallel programs running on computer cluster, and it would be desirable if programmers can optimize the communication by hand; however, that extra work would make the programming task less systematic, more complex, and error prone. We introduce several techniques to deal with these general problems of run-time performance, which may widely present in other bioengineering applications. Methods to reduce the programming task and to allow programmers to focus more on computation logic are also proposed.

#### 1.1 Motivation

Fundamental biology has achieved incredibly significant advancement in the past few decades, especially at the molecular, cellular, and genomic levels. This advancement results in dramatic increase in fundamental information and data on mechanistic underpinnings of biological systems and activities. The real challenge is now how to integrate information from as low as genetic levels to high levels of system organization. Achievement of this will help both scientific understanding and development of new biotechnologies. Engineering approaches - based on physics and chemistry and characterized by measurement, modelling, and manipulation - have been playing an important role in the synthesis and integration of information. The

combination of biological science research and engineering discipline has resulted in the fast growing area of biomedical engineering, which is also known as bioengineering.

Of the many methods of engineering principles, computational and numerical methods have been receiving increasing emphasis in recent years. This is mainly because of its physics and chemistry root, as well as the recent advancement of computing technologies, which makes complex computation feasible, cost-efficient and less time-consuming. As a result, computational bioengineering, which employs computational and numerical methods in bioengineering research and industry, has experienced fast adoption and development in the last few years.

The complex nature of biological system contributes to the large computation complexity of these problems. Another important characteristic is the distribution of data and instruments. These together inspire the use of parallel and distributed computing in computational bioengineering. With this computing technique, a single large-scale problem can be solved by dividing into smaller pieces to be handled by several parallel processors, and by taking advantage of distributed specialized computation resources, such as data sources and visualization instruments.

However, there are several challenges involved in using parallel and distributed techniques in computational bioengineering. Firstly, efficient programs utilizing parallel and distributed technique are far from easy development, especially for medical doctors and practitioners whose trainings are not computer programming. This is because programmers of parallel and distributed system, in addition to specifying what values the program computes, usually need to specify how the machine should organize the computation. In other words, programmers need to make

decision on algorithms as well as strategies of parallel execution. There are many aspects to parallel execution of a program: to create threads, to start thread execution on a processor, to control data transfer data among processors, and to synchronize threads. Managing all these aspects properly on top of constructing a correct and efficient algorithm is what makes parallel programming so hard.

When a computer cluster, the most popular and accessible parallel computing facility, is used as the hardware platform, the relatively larger communication latency is a further obstacle in achieving high performance. Practical experience usually shows a threshold of the number of processors, beyond which the performance starts degrading with larger number of processors.

Another important performance criterion, especially for clinical applications, is whether a system is capable of supporting real-time operation. When this is concerned, in addition to computing capacity, latency or lag, defined as the time it takes to get the result after the input is available for the processing system, imposes further performance requirements. When parallel computing is used, the coordination among participating processors, although increases the computing capacity, will result in larger latency.

There is also the challenge from the fact that biomedical engineering is a fast evolving field, with dozens of methods available for each task, and with new methods invented every day. It would be desirable to separate the computational logic from the supporting code, such as thread creation and communication. Parallel processing also complicates this task and computational logic is often tightly coupled with supporting code, making it difficult for non-computer experts to customize the methods to use.

Based on the aforementioned observations, the main research objectives of this thesis are summarized as follows:

- Identify typical performance bottlenecks, especially when common hardware platforms and software environments are used and when typical computational bioengineering applications are concerned;

- Derive methods to solve the above performance problems, without largely complicating the programming task, to introduce complex tools, or to add more overhead;

- Derive methods to achieve real-time processing for specific biomedical application. These methods should be scalable to larger problem size or higher precision of results; and

- Derive methods to achieve core computational logic customizability. This

is the best way to reduce programming workload of non-computer

medical personnels facing similar programming tasks.

#### 1.2 Thesis Contributions

Our research activities are based on two representative computational bioengineering applications, namely numerical simulations of fiber suspension modelling, and laser speckle image processing for blood flow monitoring. We study how high-performance parallel programs can be built on computer clusters for these applications, with consideration of the special characteristics of this platform.

Fiber suspension simulation is a typical numerical simulation problem similar to N-body problem. Parallel processing technique is used to support larger domain of simulation and thus provides more valid results. With specific problem scale, parallel processing will largely reduce time to acquire simulation result. A computer cluster will be used to perform the computing task. Parallelization is accomplished by spatial decomposition. Each spatial subdomain will be assigned to a parallel process for individual simulation. Neighboring subdomains usually have interactions and need to exchange data frequently. The need for data exchange implies that communication latency will be a significant factor in affecting the overall performance. The idea of using parallel computing to solve this type of problems is not new. However, there is little research done on identifying the bottleneck of performance improvement and optimizing the performance on computer cluster platform. In our research, theoretical analysis, simulations and practical experiments all show that communication latency will increasingly hinder the performance gain when more parallel processors are used. Communication overlap is proved to effectively solve this communication latency problem. This conclusion is supported by both theoretical analysis and realistic experiments.

Laser speckle image processing is chosen as a representative application of biomedical image processing. A large portion of biomedical image processing problems share the important common feature of spatial decomposability, which means the image can be segmented into blocks and processed independently. Although there is little interaction among these blocks, image processing usually requires real-time processing. The second part of the thesis is contributed to the parallel processing of biomedical images using a computer cluster, the most accessible parallel platform. We build a master-worker framework to support this

application family, and build support for real-time processing inside this framework. This framework is simple, highly customizable and portable, and natively supports computer clusters. Potential limitations to real-time processing are analysed and solution is proposed. As a demonstration, real-time laser speckle image processing is implemented. The image processing logic can easily be customized, even in other languages, and this framework for parallel image processing can be easily incorporated into other image processing tasks. Since our framework is portable, it can be used on various types of parallel computers besides the computer cluster, which our implementation is based on.

In summary, we have achieved the following:

- We have found and verified that asynchronism among parallel processes of the same task is a main source of communication latency. This type of communication latency is among the most common types of performance, especially for applications similar to fiber suspension simulation. This latency is independent of communication networking technology used and cannot be reduced by improvement on interconnection networks.

- We have shown why and how communication overlap can help reduce the negative impact of communication latency, including both network-related and asynchronism-related latencies. We have also demonstrated how communication overlap can be implemented with MPICH with p4 device, which does not support real non-blocking data communication. Using this implementation, we have largely improved performance of fiber suspension simulation, and enable more processors to be used without performance degradation.

- We have demonstrated how parallel real-time image processing can be

achieved on a computer cluster. The computational logic is also

customizable, allowing researchers to use different methods and

configuration without rewriting the whole program.

- We have designed a simple, scalable, and portable application framework for real-time image processing tasks similar to laser speckle image processing. Our design effectively separates processing logic from the underlying system details, and enables the application to harness different platforms and probably future parallel computing facilities without program modification.

#### 1.3 Thesis Outline

This paper is divided into four parts, as described in the following paragraphs.

The first part comprises of this introduction, a short introduction to parallel computing, a description of the prototype problems, and the hardware platform and software environment used in this research. This part covers from Chapter 1 to Chapter 3.

The second part, consisting of Chapter 4, focuses on first type of problem, the fiber suspension simulation problem. This is treated as a representative Computational Fluid Dynamics problem, one of the most common problem types in computational bioengineering field. This part describes the common algorithm

skeleton and generic parallel execution strategies, which are optimized for solving this iterative problem on computer clusters.

The third part, consisting of Chapter 5, focuses on another prototype problem, the parallel processing of speckle images. Image processing is another common problem in bioengineering. It usually features large input and output data as well as large computational complexity. The results after processing, including the laser speckle images, would be much more meaningful if they can be obtained in real-time. This need raises even more rigorous performance requirement. This part describes the effort to use computer cluster to tackle this problem. Some properties of this type of problems prevents computer cluster to be an effective platform. Suggestions on how to tackle this difficulty is presented.

In the last part, Chapter 6, a summary is given. Based on the discussion in part 2 and 3, suggestions on interesting future improvement will also be presented.

# **Chapter 2 Background**

Parallel and distributed computing is a complex and fast evolving research area. In its short 50-year history, the mainstream parallel computer architecture has evolved from Single Instruction Multiple Data stream (SIMD) to Multiple Instructions Multiple Data stream (MIMD), and further to loosely-coupled computer cluster; now it is about to enter the Computational Grid epoch. The algorithm research has also changed accordingly over the years. However, the basic principles of parallel computing, such as inter-process and inter-processor communication schemes, parallelism methods and performance model, remain the same. In this chapter, a short introduction of parallel and distributed computing will be given, which will cover the definition, motivation, various types of models for abstraction, and recent trend in mainstream parallel computing. At the end of this chapter, the connection between parallel computing and bioengineering will also be established. Materials given in this chapter server as an overview of technology development and will not be discussed in details. Readers will be advised to relevant materials for further information.

# 2.1 Definition: Distributed and Parallel Computing

Distributed computing is the process of aggregating the power of several computing entities, which are logically distributed and may even be geologically

distributed, to collaboratively run a single computational task in a transparent and coherent way, so that they appear as a single, centralized system.

Parallel computing is the simultaneous execution of the same task on multiple processors in order to obtain faster results. It is widely accepted that parallel computing is a branch of distributed computing, and puts the emphasis on generating large computing power by employing multiple processing entities simultaneously for a single computation task. These multiple processing entities can be a multiprocessor system, which consists of multiple processors in a single machine connected by bus or switch networks, or a multicomputer system, which consists of several independent computers interconnected by telecommunication networks or computer networks.

Besides in parallel computing, distributed computing has also gained significant development in enterprise computing. The main difference between enterprise distributed computing and parallel distributed computing is that the former mainly targets on integration of distributed resources to collaboratively finish some task, while the later targets on utilizing multiple processors simultaneously to finish a task as fast as possible. In this thesis, because we focus on high performance computing using parallel distributed computing, we will not cover enterprise distributed computing, and we will use the term "Parallel Computing".

# 2.2 Motivation of Parallel Computing

The main purpose of doing parallel computing is to solve problems *faster* or to solve *larger* problems.

Parallel computing is widely used to reduce the computation time for complex tasks. Many industrial and scientific research and practice involve complex large-scale computation, which without parallel computers would take years and even tens of years to compute. It is more than desirable to have the results available as soon as possible, and for many applications, late results often imply useless results. A typical example is weather forecast, which features uncommonly complex computation and large dataset. It also has strict timing requirement, because of its forecast nature.

Parallel computers are also used in many areas to achieve larger problem scale. Take Computational Fluid Dynamics (CFD) for an example. While a serial computer can work on one unit area, a parallel computer with N processors can work on N units of area, or to achieve N times of resolution on the same unit area. In numeric simulation, larger resolution will help reduce errors, which are inevitable in floating point calculation; larger problem domain often means more analogy with realistic experiment and better simulation result.

As predicted by Moore's Law [1], the computing capability of single processor has experienced exponential increase. This has been shown in incredible advancement in microcomputers in the last few decades. Performance of a today desktop PC costing a few hundred dollars can easily surpass that of million-dollar parallel supercomputer built in the 1960s. It might be argued that parallel computer will phase out with this increase of single chip processing capability. However, 3 main factors have been pushing parallel computing technology into further development.

First, although some commentators have speculated that sooner or later serial computers will meet or exceed any conceivable need for computation, this is only true for some problems. There are others where exponential increases in processing power

are matched or exceeded by exponential increases in complexity as the problem size increases. There are also new problems arising to challenge the extreme computing capacity. Parallel computers are still the widely-used and often only solutions to tackle these problems.

Second, at least with current technologies, the exponential increase in serial computer performance cannot continue for ever, because of physical limitations to the integration density of chips. In fact, the foreseeable physical limitations will be reached soon and there is already a sign of slow down in pace of single-chip performance growth. Major microprocessor venders have run out of room with most of their traditional approaches to boosting CPU performance-driving clock speeds and straight-line instruction throughput higher. Further improvement in performance will rely more on architecture innovation, including parallel processing. Intel and AMD have already incorporated hyperthreading and multicore architectures in their latest offering [2].

Finally, generating the same computing power, single-processor machine will always be much more expensive then parallel computer. The cost of single CPU grows faster than linearly with speed. With recent technology, hardware of parallel computers are easy to build with off-the-shelf components and processors, reducing the development time and cost. Thus parallel computers, especially those built from off-the-shelf components, can have their cost grow linearly with speed. It is also much easier to scale the processing power with parallel computer. Most recent technology even supports to use old computers and shared component to be part of parallel machine and further reduces the cost. With the further decrease in

development cost of parallel computing software, the only impediment to fast adoption of parallel computing will be eliminated.

### 2.3 Theoretical Model of Parallel Computing

A machine model is an abstract of realistic machines ignoring some trivial issues which usually differ from one machine to another. A proper theoretical model is important for algorithm design and analysis, because a model is a common platform to compare different algorithms and because algorithms can often be shared among many physical machines despite their architectural differences. In the parallel computing context, a model of parallel machine will allow algorithm designers and implementers to ignore issues such as synchronization and communication methods and to focus on exploitation of concurrency.

The widely-used theoretic model of parallel computers is Parallel Random Access Machine (PRAM). A simple PRAM capable of doing add and subtract operation is described in Fortune's paper [3]. A PRAM is an extension to traditional Random Access Machine (RAM) model used to serial computation. It includes a set of processors, each with its own PC counter and a local memory and can perform computation independently. All processors communicate via a shared global memory and processor activation mechanism similar to UNIX process *fork*ing. Initially only one processor is active, which will activate other processors; and these new processors will further activate more processors. The execution finishes when the root processor executes a HALT instruction. Readers are advised to read the original paper for a detailed description.

Such a theoretic machine, although far from complete from a practical perspective, provides most details needed for algorithm design and analysis. Each processor has its own local memory for computation, while a global memory is provided for inter-processor communication. Indirect addressing is supported to largely increase the flexibility. Using FORK instruction, a central root processor can recursively activate a hierarchical processor family; each newly created processor starts with a base built by its parent processor. Since each processor is able to read from the input registers, task division can be accomplished. Such a theoretical model inspires many realistic hardware and software systems, such as PVM [4] introduced later in this thesis.

## 2.4 Architectural Models of Parallel Computer

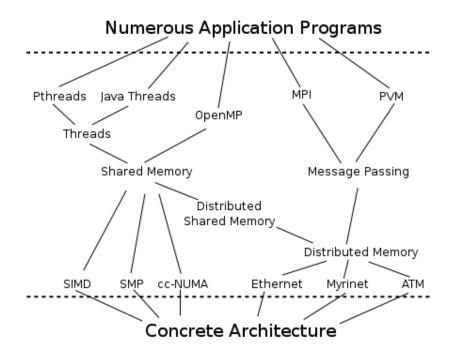

Despite a single standard theoretical model, there exist a number of architectures for parallel computer. Diversity of models is partially shown in Figure 2-1. This subsection will briefly cover the classification of parallel computers based on their hardware architectures. One classification scheme, based on memory architecture, classifies parallel machines into Shared Memory architecture and Distributed Memory architecture; another famous scheme, based on observation of instruction and data streams, classifies parallel machines according to Flynn's taxonomy.

Figure 2-1 A simplified view of the parallel computing model hierarchy

#### 2.4.1 Shared Memory and Distributed Memory

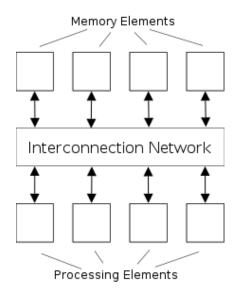

Shared Memory architecture features a central memory bank, with all processors and this memory bank inter-connected through high-speed network, as shown in Figure 2-2. Shared Memory shares a lot of properties with PRAM model, because of which it was favoured by early algorithm designers and programmers. Furthermore, because the memory organization is the same as in the sequential programming models and the programmers need not deal with data distribution and communication details, shared memory architecture has certain advantage in programmability. However, no realistic shared-memory high-performance machine have been built, because no one has yet designed a scalable shared memory that allows large number of processors to simultaneously access different locations in constant time. Having a centralized memory bank implies that no processor can access it with high speed.

Figure 2-2 Diagram illustration of shared-memory architecture

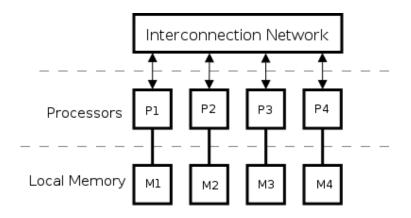

In Distributed Memory architecture, every processor has its own memory component that it can access via very high speed, as shown in Figure 2-3. Accessing memory owned by other processor requires explicit communication with the owner processor. Distributed Memory architecture uses message-passing model for programming. Since it allows programs to be optimized to take advantage of locality, by putting frequently-used data in local memory and reducing remote memory access, programs can often acquire very high performance. However, it imposes a heavy burden on the programmers, who is responsible for managing all details of data distribution and task scheduling, as well as communication between tasks.

Figure 2-3 Diagram illustration of distributed memory architecture

To combine the performance advantage of Distributed Memory architecture to the ease of programming of Shared Memory architecture, Virtual Shared Memory, or Distributed Shared Memory (DSM) system, is built on top of Distributed Memory architecture and exposes a Shared Memory programming interface. DSM virtualizes the distributed memory as an integrated shared memory for upper layer applications. Mapping from remote memory access to message passing is done by communication library, and thus programmers are hidden from message communication details underneath. Nevertheless, for the foreseeable future, use of such paradigm is discouraged for efficiency-critical applications. Hiding locality of memory access away from programmers will lead to inefficient access to memory and poor performance until significant improvements have been gained in optimization.

The most common type of parallel computers, computer clusters, belongs to the distributed memory family. With different programming tools, the programmers might be exposed to a distributed memory system or a shared memory system. For example, using message passing programming paradigm, the programmers will have to do inter-process communication explicitly by sending and receiving message, and

are based on the distributed memory architecture; but when a distributed shared memory library such as TreadMarks is used, the distributed memory nature will be hidden from the programmer. As discussed above, we would suggest the use of message passing over distributed shared memory, because communication overhead can be more significant in computer clusters. It is advantageous to allow the programmer to control the details of communication in a message passing system. This will be further discussed in Section 2.7.

#### 2.4.2 Flynn's Taxonomy

Another classification scheme is based on taxonomy of computer architecture firstly proposed by Michael Flynn [5] in 1966. Flynn differentiated parallel computer architectures with respect to number of data streams and that of instruction streams. According to Flynn, computer architectures can be classified into 4 categories, namely Single Instruction Single Data Stream (SISD), Single Instruction Multiple Data Stream (SIMD), Multiple Instruction Single Data Stream (MISD), and Multiple Instruction Multiple Data Stream (MIMD). This work was later referred to as Flynn's taxonomy.

In Flynn's taxonomy, normal sequential von Neumann architecture machine, which has dominated computing since its inception, is classified as SISD. MISD is a theoretical architecture with no realistic implementation.

SIMD machine consists of a number of identical processors proceeding in a lock step synchronism, executing the same instruction on their own data. SIMD was the major type of parallel computer before 1980s, when the computing capability of a

single processor is very limited. Nowadays, SIMD computing is only seen inside general purpose processors, as an extension to carry out vector computation commonly used, for example, in multimedia applications.

MIMD is the most commonly used parallel computers now, and covers a wide range of interconnection schemes, processor types, and architectures. The basic idea of MIMD is that each processor operates independent of the others, potentially running different programs and asynchronous progresses. MIMD may not necessarily mean writing multiple programs for multiple processors. The Single Program Multiple Data (SPMD) style of parallel computing is widely used in MIMD computers. Using SPMD, a single program is deployed to multiple processors on MIMD computers. Although these processors run the same program, they may not necessarily be synchronized at instruction level; and different environments and different data to work on may possibly result in instruction streams being carried out on different processors. Thus SPMD is simply a easy way to write programs for MIMD computers.

It is obvious that computer cluster is a type of MIMD computer. Most parallel programs on computer cluster are developed in the SPMD style. The same program image is used on each parallel processor, and each processor goes through a different execution path based on its unique processor ID.

A relevant topic is the concept of granularity of parallelism, which describes the size of a computational unit being a single "atom" of work assigned to a processor. In modern MIMD system, the granularity is much coarser, driven by the desire to reduce the relatively expensive communication.

## 2.5 Performance Models of Parallel Computing Systems

#### 2.5.1 Speedup, Efficiency and Scalability

In order to demonstrate the effectiveness of parallel processing for a problem on some platform, several concepts have been defined. These concepts will be used in later chapters to evaluate the effectiveness of parallel programs. These include speedup, which describes performance improvement in terms of time savings, efficiency, which considers both benefit and cost, and scalability, which represents how well an algorithm or piece of hardware performs as more processors are added.

Speedup is a first-hand performance evaluation. However, it is a controversial concept, which can be defined in a variety of ways. Generally speaking, speedup describes performance achievement by comparing the time needed to solve the problem on N processors with the time needed on a single processor. This is shown as:

$$S(n) = T(1) / T(n);$$

(2-1)

where S(n) is the speedup achieved with n processors, T(1) is the time required on a single processor, and T(n) is the time required on N processors. The discrepancies arise as to how the timings should be measured, and what algorithms to be used for different numbers of processors. A widely accepted method is to use optimal algorithms for any number of processors. However, in reality, optimal algorithm is hard to implement; even if it is implemented, the implementation may not perform

optimally because of other machine-dependent and realistic factors, such as cache efficiency inside CPU.

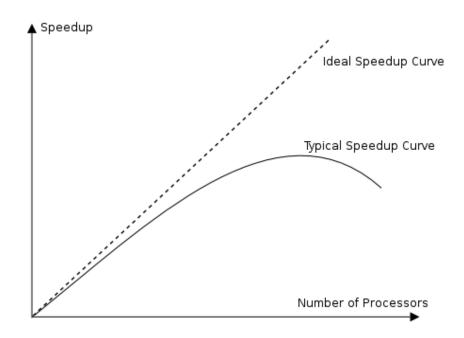

A typical speedup curve for a fixed size problem is shown in Figure 2-4. As the number of processors increases, speedup also increases until a saturation point is reached. Beyond this point, adding more processors will not bring further performance gain. This is the combined result of 1) reduced computation on participating node, and 2) increased duplicate computation and synchronization and communication overhead.

Figure 2-4 Typical speedup curve

The concept of *efficiency* is defined as

$$E(n) = S(n) / n. ag{2-2}$$

It measures how much speedup is brought per additional processor. Based on the typical speedup curve shown in the figure above, it is evident that typically efficiency will be decreased upon increase in the number of processors.

The concept of *scalability* cannot be computed but evaluated. A parallel system is said to be scalable when the algorithm and/or the hardware can easily incorporate and take advantage of more processors. This term is viewed as nebulous [6], since it depends on the target problem, algorithm applied, hardware, current system load, and numerous other factors. Generally, programs and hardware are said to be scalable when they can take advantage of hundreds or even thousands of processors.

In practice, the computable speedup and efficiency can be much more complex. Both values are affected by many factors, which can be algorithmic and practical. Take superlinear speedup as an example. Superlinear speedup is defined as the speedup that exceeds the number of processors used. It is proved that superlinear speedup is not achievable in homogeneous parallel computers. However, when heterogeneous parallel computers are used, it is possible to achieve it [7]. An example of practical factors that may lead to superlinear speedup is cache performance: when a large number of processors are used, problem scale on a single node is largely reduced, which may result in higher cache hit ratio, fast execution, and finally probably superlinear speedup even if communication overhead is not negligible. When the parallel computer is not dedicated to a single parallel computing task, load difference among the computing nodes will imply heterogeneity and consequently the possibility of superlinear speedup. That is what we will encounter in later chapters.

#### 2.5.2 Amdahl's Law

As shown in the previous subsection, efficiency gets reduced as more processors are added. This effect implies the limit of parallel performance: when the number of processors reaches some threshold, adding more processors will no longer generate further performance improvement and will even result in performance degradation, due to decrease in time saving brought by further division of task and increase in overhead of interprocess communication and duplicate computation. Gene Amdahl presents a fairly simple analysis on this [8], which is later referred to as Amdahl's Law.

Amdahl gave the speedup of a parallel program as:

$$S(n) = \frac{1}{s + \frac{p}{n}} < \frac{1}{s}.$$

(2-8)

where p is the fraction of code that is parallelizable, and s=1-p, is that requires serial execution. This inequality implies that superlinear speedup is not achievable and the maximal ideal speedup cannot exceed  $\frac{1}{s}$ , where s is the ratio of serial code (i.e., the code that requires serial execution) out of the whole program.

Amdahl's Law is a rough method to evaluate how parallel computing can be effective for a specific problem. Amdahl's Law has resulted in pessimistic view of parallel processing. For example, if 10% of the task must be computed using serial

computation, the maximal ideal speedup is 10. Since 1967, Amdahl's Law was used as an argument against massively parallel processing (MPP).

Gustafson's discovery [9] on loophole of Amdahl's law has led the parallel computing field out of pessimism and skepticism. Since then, the so-called Gustafson's Law has been used to justify MPP. Amdahl assumed the problem size to be fixed as the number of processors changes, and thus s and p to be constants. In many scientific applications, problem size is flexible, and when more processors are available, problem size can be increased in order to achieve finer result such as higher resolution or higher precision. To quote Gustafson, "speedup should be measured by scaling the problem to the number of processors, not fixing problem size." When problem size is changed, s and p are no longer constants, and the limit set by Amdahl's Law is broken.

According to Gustafson's observation, the amount of work that can be done in parallel varies linearly with the number of processors and the amount of serial work, mostly vector startup, program loading, serial bottlenecks and I/O, does not grow with problem size. Use s' and p' to represent execution time associated with serial code and parallel code, rather than ratio, spent on the *parallel* system with n homogeneous processors, then if this task is to be computed on a single processor, the time needed can be represented as:

$$T(1) = s' + np',$$

(2-9)

and the *scaled* speedup can be written as:

$$s'(n) = \frac{T(1)}{T(n)} = \frac{(s'+np')}{s'+p'} = n - (n-1) \cdot \frac{s'}{s'+p'} = n - (n-1) \cdot s'', \tag{2-10}$$

if s'' is defined as s''(s'+p'). s'' is the ratio of serial code, but has different meaning from the ratio s in Amdahl's Law: s'' is the ratio of serial code with reference to whole program executed on *one* processor in a *parallel* execution, while s is with reference to all code in the whole program for the problem [10]. It must also be noted that s is a constant that is only relevant to the computation problem, under the precondition that problem scale is fixed; while s'' is a constant under the precondition of problem scale changes as Gustafson described. Under Gustafson's Law, the speedup can be linearly increased with the number of processors hired in the computation.

In the context of computational bioengineering, Gustafson's Law makes more sense than Amdahl's Law, because with larger computing capability, it is desirable to acquire better result, in terms of resolution in image processing and simulation and in terms of higher precision in many numerical applications. When the problem size is fixed, Amdahl's Law has told us to reduce the fraction of code that has to be executed in serial. Essentially, we have to reduce the fraction of code whose execution time cannot be reduced by introducing more processors. Since communication code has this feature, we will look into the techniques to optimize inter-processor communication.

## 2.6 Interconnection Schemes of Parallel Computing

## **Systems**

Both Amdahl's Law and Gustafson's Law acknowledge the significance of serial code in affecting the parallel computer performance. Another important factor that is closely related to parallel program performance is inter-process communication and synchronization. Especially with modern technology, processing capability of single chip has been tremendously increased; however, inter-process communication has received relatively small improvement, and thus become the bottleneck of overall performance. That also explains the trend of coarser-granularity parallelism. High-performance parallel computers, especially those able to scale to thousands of processors, have been using sophisticated interconnection schemes. Here we cover the major interconnection schemes listed in Figure 2-5 in brief.

Figure 2-5 Illustrations of Simple interconnection schemes

Figure 2-5(A) illustrates the *line* scheme, which is the simplest connection scheme. In this illustration, circle represents a computing node and line represents direct communication channel between nodes. Computing nodes are arranged on and connected with a single line. Except for the nodes at the two ends, vertex degrees are all 2 and thus the implementation of network interface is simple; routing is simple and the topology can be viewed as recursive. However, communication between any two non-neighbor nodes needs the help of other nodes; the connectivity is only 1 and fault at any node will make the whole system break; and diameter of this corresponding graph is *n*-1, where *n* is the number of nodes, which implies that the latency could be very high. To summarize, this scheme is simple and low-cost, but will not be able to generate high performance or reliability; and as system scales, the performance degrades rapidly.

Figure 2-5(B) illustrates the *ring* scheme, which is an enhanced line topology, with an extra connection between the two ends of the line. This increases the

connectivity to 2 and decreases the diameter to half of the corresponding line topology. However, basic characteristics are still the same.

The other extreme is probably the *fully-connected* topology, in which there is a direct connection between any two computing nodes. Fully-connected topology is shown in Figure 2-5(C). The corresponding graph representation has an edge between any two vertices, and distance between any two vertices is 1. Thus the diameter is 1, and it generates the minimal communication latency, if the physical link implementation is fixed, as well as the maximal connectivity. However, the degree of nodes changes with the number of processors and thus the implementation of network interface must be very complex; and it is hard to be recursive, adding another layer of complexity of implementation and reducing the scalability. To summarize, this scheme will generate the highest performance possible, but due to the complexity and thus cost, it can hardly be scalable: with larger scale, although performance will not degrade at all, complexity will climb very fast at the level of  $O(n^2)$ .

Similar to fully-connected network, *bus* network, illustrated in Figure 2-5(E), has direct connection between any two nodes. In fact, bus topology shares the same logical graph representation with fully-connected topology and. Consequently, static characteristics of bus topology are exactly the same as those of fully-connected topology. But connection between any pair of nodes is not dedicated but shared: interconnection is implemented via a shared bus. This reduces the complexity significantly. In fact, its complexity is similar to that of line and ring topology. However, the dynamic characteristics, such as data transfer speed, are more inferior to those of fully-connected counterpart. Although collective communication is now very easy to implement, this single shared bus prevents more than one pair of nodes to

carry out point-to-point communication. As a result, the system does not scale very well.

An intuitive improvement on bus network is to change the bus to eliminate the constraint that only two nodes can communicate at any time. The result is the *star* network, where a communication switch node is added to replace the shared bus, as shown in Figure 2-5(D). If we treat this switch node as a non-computing node and ignore it in the graph representation, then star network corresponds to the same fully-connected graph as bus network, while the implementation does not have the constraint of bus network; if switch node is viewed as normal computing node, then the corresponding graph has a diameter of 2, supports easy implementation of collective communication with the help of the central switch node, and allows recursive expansion. Except for the switch node, all other nodes have a constant vertex degree of 1. The critical disadvantage is that the connectivity is 1: failure at the switch node will cause the whole system to fail.

For computer clusters, most are built with a star structured interconnection network around a central switch. For better fault tolerance or easier setup, the other interconnection scheme might also be used. Parallel program using message passing might be rewritten to better adapt to different interconnection network.

There are other types of more sophisticated topology schemes, such as tree, mesh, and hypercube, which are widely used in parallel computers with thousands of processors or more. These schemes often scale better to larger scale network with good performance. Readers are advised to [11] for more information about this.

## 2.7 Programming Models of Parallel Computing

## **Systems**

Programming models are high-level abstract views of technologies and applications that hide most architectural details with programmers as the main audience. For MIMD machine like a computer cluster, the most important models include shared-memory model, message passing model, and object oriented model.

In the shared-memory model, multiple tasks run in parallel. These tasks communicate with one another by writing to and reading from a shared memory. Shared-memory programming is comfortable for the programmers, because the memory organization is similar as in the familiar sequential programming models, and programmers need not deal with data distribution or communication details. Popularity of this model was also promoted by its similarity to the theoretical PRAM model. Practice of programming on this model originated from concurrent programming on transparency of data and task placement determines that, besides the simplicity of programming, the performance cannot be predicted or controlled on hardware platform with Non-Uniform Memory Architecture (NUMA) or distributed memory. This performance problem is evident especially on large-scale multiprocessor systems, in which access time to memory at different locations varies significantly and thus memory locality plays critical role in determining overall system performance.

Message passing model is becoming the prevailing programming model for parallel computing system, thanks to the trend to large-scale multiprocessors systems, including computer clusters. In this model, several processes run in parallel and communicate and synchronize with one another by explicitly sending and receiving message. These processes do not have access to a shared memory or a global address space. Although harder to program compared to previous models, it allows programs to explicitly guide the execution by controlling data and task distribution details. Since everything is under the programmer's control, the programmer can achieve close to optimum performance if enough effort has been spent on performance tuning. Besides this performance advantage, message passing model is also versatile. Being a relatively low-level model, it is capable of implementing many higher-level models. A typical example is the widely-used SPMD data model, which fits in with many naturally data-parallel scientific applications. Very low-level message passing systems, such as Active Message, are even used to implement shared-memory system by emulating a shared memory. These systems, while allowing easy high-level algorithm design with the help of more friendly high-level models, expose enough low-level details to support and encourage the programmers to manually control and tune the performance. Wide deployment of multicomputers and loosely-coupled computer clusters, which feature expensive communication, promotes the popularity of message passing systems. Message Passing Interface (MPI) [12] and Parallel Virtual Machine (PVM) [4] are the 2 major programming libraries used to build message passing system. MPI is the base of our research and will be covered in detail in the next chapter.

In this chapter, we have reviewed some basic concepts in parallel computing systems. Parallel computing is the simultaneous execution of the same task on

multiple processors in order to obtain faster results. It is used to acquire the results faster and/or to acquire better results, which is useful in many computational bioengineering applications. PRAM is the model of parallel computer to study the algorithm, and in practice, program designers usually have to consider the architectural models of the hardware to better utilize the resources available and to achieve higher performance. In this context, computer cluster belongs to distributed memory MIMD computers. To evaluate the performance, several terms have been defined. Studies on these terms suggest the important role of inter-processor communication. That is why many different interconnection schemes with different levels of complexity have been devised. Computer cluster usually uses the star-structured scheme, but more complex scheme may be employed when the cluster scales to a larger size. We have shown that to have better control on the execution details including inter-processor communication, message passing programming model is suggested.

In the next chapter, we will look into the architecture and programming model used in our research with more details.

## Chapter 3 Overview of Hardware Platform and

#### Software Environments for Research in

## **Computational Bioengineering**

In this chapter, we will focus on hardware and software platforms we use in our research. As for hardware, 3 types of platforms with message passing architecture are involved in our research, to best take advantage of available resources and to satisfy different requirements. As for software tools, message passing is the main programming paradigm used, and *Message Passing Interface* (MPI) model and library are used in both research projects. For image processing algorithms that are more suitable for SIMD-style architectures, use of SIMD extension instructions in commodity CPU are also investigated.

#### 3.1 Hardware Platform

Parallel program based on message passing paradigm can be run on various platforms, ranging from high-end distributed-memory multiprocessor systems with thousands of processors, such as IBM Blue Gene/L [13], the No. 1 supercomputer in the world as of this writing, to multicomputer system with dozens of CPUs, like the

computer cluster we use in our research. Our research projects mainly rely on a computer cluster for computing power. For the biomedical image processing project, we propose to use Computational Grid to integrate our system into other components of whole system. We also look into the possibility to utilize the vast computing power available in thousands of campus workstations connected via high-speed campus network, as well as the SIMD extension available in modern commodity CPU.

#### 3.1.1 Computer Cluster

A computer cluster is a group of loosely coupled computers that work together closely so that in many respects it can be viewed as though it were a single computer. Clusters are commonly (but not always) connected through fast local area networks. Comparing to parallel machines with specific-purpose hardware components, computer clusters use commodity general-purpose components and usually have significant cost advantage. This means that with the same amount of budget, building a computer cluster usually will result in higher system performance. With the fast increase in performance of commodity components and improvement of network technology, computer cluster is now the mainstream architecture of modern parallel machines.

The main piece of hardware used in our research is the Hydra II computer cluster system, built and maintained by *Singapore MIT Alliance* (SMA). This system consists of one dual-processor head node and 34 uni-processor client nodes, connected via a Gigabit Ethernet switch. The head node is equipped with 2 Pentium III processors, both clocked at 1.3GHz, and 2 GB of RAM. Each client node has one 1.3GHz

Pentium III processors attached with 1GB of RAM. LINPACK benchmark shows the system can generate 27GFlops of average computing power.

#### 3.1.2 Computational Grid

Grid computing is a very young and uncharted field [14]. Various definitions and designs coexist and numbers of implementations based on different designs have been built and deployed in real applications. Out of them, Computational Grid, described by Open Grid Services Architecture (OGSA) [15], standardized by Open Grid Services Infrastructure (OGSI) [16], and implemented and refined in Globus toolkit by Globus Alliance (http://www.globus.org), is widely accepted as the standard form. Computational Grid, named by analogy to electric power grid, is defined as hardware and software infrastructure that provides dependable, consistent, pervasive, and inexpensive access to high-end computational capabilities. It is hoped that inexpensive, reliable and universally accessible computing power brought by Computational Grid will result in revolutionary development of computing devices, like the electric power grid did in the 1910s. To be specific, one of the many present goals is to allow execution of parallel code across more than one supercomputer site or computer cluster.

Computational Gird is designed to integrate distributed computing power to form a single supercomputer, which would be a rather powerful *hypercomputer* to tackle large-scale computation problems. When message passing programming is to be considered, the mainstream *Message Passing Interface* (MPI) implementation, MPICH, has support for Grid-based communication. Unfortunately, in practice there are a lot of problems to be circumvented. For example, for many computer clusters,

only the head node has the public Internet Protocol (IP) address, which makes the direct Grid-based communication between 2 client nodes residing in different computer clusters impossible. When our research is to be considered, the heterogeneous nature and hierarchical structure of Gird are further barriers to efficient deployment of our flat-structured MPI program.

We use Grid mainly to take advantage of its capability to integrate different types of resources. For many computational bioengineering applications, various types of resources are involved. Take biomedical imaging as a typical example: specialpurpose imaging equipment is used to acquire the images possibly in the form of video; a powerful computer is needed to process this image information, preferably in real-time; another computer may present to perform more complex image processing in a non-real-time manner; and a storage device with large capacity may be used for data storage and enquiry. Rather than building a machine consisting of all these components, Grid can help to glue these distributed components together, some of which may already exist. Being able to reuse existing components not only means cost reduction, but also means more scalable system with more desirable functions. For example, imagine the scenario that developers have implemented a good feature in an image processing program based on a hardware platform that best suits this program. Without using Grid, when it is time to build a new system with new image capturing facility, for example, there is usually the need to migrate to a new image processing program that may not suit the application, or to rewrite the existing program on a new platform that may not suit the program. Grid can help integrate this system into a new system without the need to rewrite the program or to migrate to a new hardware platform, and best save the development effort while preserving the functionality.

In our research on parallel biomedical image processing, we look at the option of integrating speckle image processing program with image acquiring facilities using Computational Gird techniques.

#### 3.1.3 Network of Workstations

A *Network of Workstations* (NOW) is a computer network which connects several computer workstations together, and by using specific software it allows to use the network as a cluster. Different from nodes of a computer cluster, workstations of NOW is often loosely-coupled, and although they are continuously connected to the network, every workstation is not dedicated to the NOW tasks and some of them will accept tasks from normal interactive user sessions. One of the many goals of NOW is to utilize idle CPU cycles [17]. When a node is overloaded with tasks from interactive user session and is no longer idle, task distribution system of NOW will be removed from this node and be migrated to another node or simply be suspended. Since the progress of subtask is unpredictable, the NOW system is more suitable for problems that can be divided into independent subproblems. Master-worker programming model is an example of suitable models.

The first NOW system was developed at UC Berkeley [18]. As of April 1997, it was listed in the 200 fastest machines in the world, thanks to its 10 GFLOPS performance in LINPACK benchmark. In our university, workstations connected via campus network provide desirable environment to build NOW system. This is because a large portion of CPU cycles are wasted with no user task at all or with tasks requiring little CPU power; besides, all workstations are constantly connected to

high-bandwidth network; furthermore, there are also a lot of research applications suitable to run on NOW system.

Image processing is one of such applications. Non-real-time image processing that employs complex algorithms and thus requires large computing power can take advantage of this computing platform, if the algorithm allows subtasks with little interaction. Such prerequisite holds true for most image processing algorithms, which divide a large image into subimages and process them independently.

In our parallel image processing project, master-worker programming model is used, which implies that NOW system can be used to run the program. In the implementation, the design of portable communication layer allows the program to be ported to use many hardware and software platforms. We suggest future research to implement a BSD socket-based communication layer, which allows the program to run on NOW systems. If other higher-level NOW communication systems are used, such as Active Message [19], it would also be possible and easy to port onto it. Details about the design of portable communication layer will be given in Chapter 5 and relevant suggestion for future research is given in Section 6.5.

#### 3.1.4 Vector processing in commodity CPU and GPU

Major commodity microprocessor vendors have included SIMD instruction extensions in their CPU offerings. For example, Intel has added SIMD instructions since its Pentium MMX offering, and has enhanced this design through Streaming SIMD Extensions (SSE), SSE2, and SSE3, appearing respectively in Pentium III, Pentium 4, and Pentium 4 Prescott revision; the PowerPC vendors has also integrated

its floating point and integer SIMD instruction set, known as AltiVec, in both G4 and G5 CPU families. Utilizing this vector processing capability properly will largely increase the performance of some applications such as image processing.

Graphic Processing Unit (GPU), a common component available in almost every computer, is another source of vector computing power which recently starts to gain a lot of attention. There is a trend of using the GPU rather than CPU to perform computation. This technique is known as General-Purpose computation on Graphics Processing Units (GPGPU) [20] [21]. With graphics and image processing applications being the main consumer of this technique, many non-graphics areas, including cryptography, signal processing, are also benefiting from instinctive powerful vector processing capability of modern GPU.

SIMD extension and GPGPU may largely improve the performance of image processing programs, since many algorithms in this area are SIMD computation and vector processing by nature. Due to time constraint and availability of hardware and software, this technique is not covered in our research. However, it is receiving much research attention recently and may be studied in future research.

## 3.2 Software Environments for Parallel Programming

As stated in the previous chapter, parallel programming is a complex task. In order to reduce this complexity, different programming models are abstracted, with each providing tools such as special-purpose compilers, libraries and frameworks to simplify programming task. These tools hide many details about parallel execution, such as message transfer and routing, task allocation and migration, and platform

differences. Higher-level programming model will even have commonly-used algorithms pre-implemented in the bounded libraries. As an example, Fluent, a high-level programming system to develop CFD programs with parallel processing capabilities, have built in many CFD-specific functions such as dynamic meshing and acoustics modeling, which makes more like a program than a programming system. Our research is based on message passing programming model and specifically on *Message Passing Interface* (MPI) standards and MPICH library.

#### 3.2.1 Message Passing Interface and MPICH

Message Passing Interface, or MPI, is the most widely-used message passing standard. The basic functions are defined by the MPI standard [12], and with many implementations targeting almost all distributed memory architectures, it is the *de facto* industrial standard for message passing programming.

Basically, MPI provides two types of communication operations. Point-to-point operations allow any two processes to exchange information via MPI\_Send (for sending), MPI\_Recv (for receiving) and their variants. Collective operations are provided so that a set of processes, known as a *communicator*, can share and dispatch data through broadcast and reduction operations.

When an MPI program runs, the user will explicitly specify the number of parallel processes and how the processes are mapped to physical processors. On startup, each processor starts one or more processes to execute the same program body. Each parallel process will be assigned a rank, which serves as the identity of the process, and which will also cause processes to carry out different computation

despite their common program body. During the execution, processes carry their own computation, without synchronization with other processes unless they encounter an explicit synchronization command. Processes communicate with each other using point-to-point or collective communication primitives, using process rank to address the recipient or sender if it is required. The whole parallel program exits when all the parallel processes have finished. Although there is no requirement on how the computation result is generated, in many cases a head process, usually the one with rank 0, will collect the results from participating processes and assemble the final outcome.

Apart from MPI, another well-know standard for inter-process message passing is called *Parallel Virtual Machine*, or PVM [4]. One major difference between these 2 standards is that PVM provides semantics for dynamic process creation: a parallel process is capable to spawn a new process on some node. This feature resembles the PRAM model, in which a processor can activate another idle processor to join parallel processing. Because of this, PVM provides more flexibility and scalability, and is more suitable for heterogeneous environment than MPI. Unfortunately, due to lack of development effort and support, PVM suffers from performance problem and lack of important features. As MPI becomes the *de facto* standard and MPI-2 has adopted numbers of excellent features in PVM, PVM itself is fading out from the parallel programming area.

The two major implementations of MPI standards are MPICH [22] developed by Argonne National Laboratory and LAM by Ohio Supercomputing Center and Indiana University. Our research is heavily based on MPICH and its successor MPICH2. Besides a complete and efficient implementation of MPI-1 standard and partial MPI-2

standard, MPICH also targets at a portable design. Area of parallel computing features a large number of different architectures, interconnection scheme and technology, and communication protocols. This makes portability and efficiency often conflicting tasks. MPICH separates a vast set of machine independent functions from a machine specific abstract device interface (ADI), which is about lower-level communications. This design simplifies the job of porting MPICH to different architectures and platforms without much sacrifice of performance. When MPICH is to be ported to a new platform, at the beginning stage, only a small number of fundamental subroutines in ADI need to be implemented, and all other subroutines will be based on these fundamental ones and need not be rewritten. After this step, a functional MPICH is built on this platform. When more development power is available, non-fundamental subroutines in ADI can be selectively reimplemented to take advantage of platform features, and thus performance can be gradually improved. Thanks to this portable design, MPICH has been adopted by almost all major vendors, including IBM, HP, SGI, and SUN, all of which has built their own so-called native MPICH implementation which leverages their hardware features. For example, MPI implementation on IBM Blue Gene/L is based on MPICH and utilizes the platformspecific design of dedicated *collective network* in its ADI implementation to support efficient broadcast and reduction operations [23].

MPICH2 is an all-new implementation of MPI by the MPICH team. In addition to features of its predecessor, including the portability advantage, MPICH2 includes partial implementation of MPI-2 functions, including one-side communication, dynamic process creation, and expand MPI-IO functionality. One important improvement for our research is that MPICH2 has better support for multithreading. This makes it safe to run another thread for computation while the main thread is busy

with inter-process communication, which is just the idea of communication-computation-overlap covered in Chapter 4.

#### **3.2.2 Vector Processing Software**

Intel provides a set of tools to allow programmer to take advantage of its SSE instruction extension. These tools are provided in forms of new assemblers to understand these extended assembly instructions, dedicated C intrinsic functions, and compiler capable of doing automatic vectorization. Although these tools and techniques are not used in our research due to our focus on programming framework and the relatively simple algorithms we choose for image processing, they may be important for other applications using more complex algorithms.

As for GPGPU, because computing capabilities of different GPU chips differ significantly, programs using GPGPU can hardly be portable. Our research will not use this technology. More information about this technology can be found on the GPGPU website [24] and Fernando's *GPU Gems* [25].