entity CIRCUIT is

port( A,B,C,D: in bit; -- A,B,C,D are inputs

O: out bit); -- O is the output

end CIRCUIT;

architecture str of CIRCUIT is

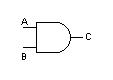

component AND2 is -- This design will use our AND2 that

port( A, B: in bit; -- we wrote above. So we must include

C: out bit); -- it as a component.

end component;

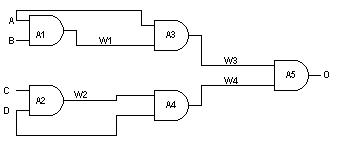

signal W1,W2,W3,W4: bit; -- signals W1-W4 represent internal

-- wires to our circuit.

begin

A1: AND2 port map(A,B,W1); -- AND2 takes A,B, outputs W1

A2: AND2 port map(C,D,W2); -- AND2 takes C,D, outputs W2

A3: AND2 port map(A,W1,W3); -- AND2 takes A,W1, outputs W3

A4: AND2 port map(W2,D,W4); -- AND2 takes W2,D, outputs W4

A5: AND2 port map(W3,W4,O); -- AND2 takes W3,W4, outputs O

end str;

Our circuit has four inputs and a single output. Since we are reusing our AND2 entity, we must include it as a component. Then we create four signals, in this case they can be thought of as wires internal to our circuit. We place five seperate AND2 units in our circuit. The paramaters sent to each AND2 represent the inputs and output of each. For example, the input to A1 will be the A and B inputs, and the output will be W1. We can see that the circuit we created in VHDL mirrors the circuit in the image above.