## COMPUTER

## Fast Secure Processor for Inhibiting Software Piracy and Tampering

Jun Yang, Youtao Zhang\*, and Lan Gao University of California, Riverside \*University of Texas at Dallas

**ORIVERSIDE**

## Outline Motivation XOM Architecture Overview Offloading Crypto-Computation from Critical Path Architecture Design Experiment Evaluation Summary

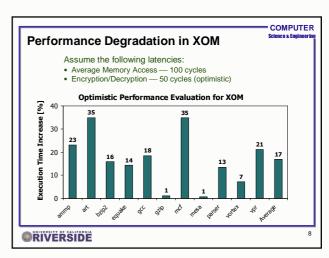

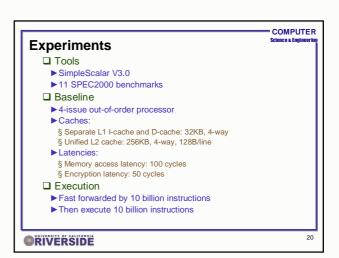

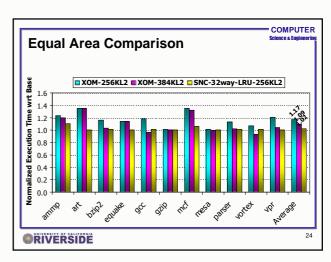

## Other Experiments ☐ SNC Induced Memory Traffic ► On average, there is only 0.31% of the L2 memory traffic posed by SNC replacements on to the system bus ☐ Sensitivity to Encryption Latency ► XOM degrades greatly from 16.7% to 34.2% slowdown ► The performance of our design with LRU replacements is almost unchanged