All-Digital Quadrature Modem for High Speed Wireless Communications

Email: amitra@cs.ucr.edu

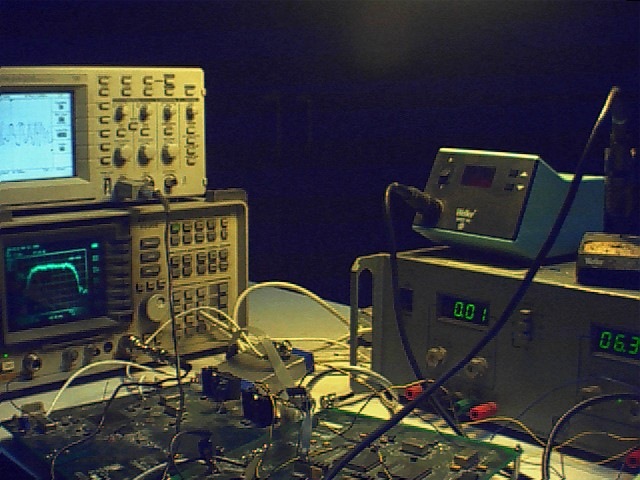

Some Other Images (useful for your next project presentation ;) )

A VLSI Architecture for a High-Speed All-Digital Quadrature Modulator and Demodulator for Digital Radio Applications. ”Henry Samueli and Bennett C. Wong”, IEEE Journal on Selected Areas in Communications, Vol8, No 8, October ‘90

A BPSK / QPSK Timing – Error Detector for Sampled Receivers. “Floyd M Gardner”, IEEE Transactions on Communications, Vol. COM-34, No 5, May ‘86

A survey of CORDIC algorithms for FPGA based computers. “Ray Andraka”, FPGA 98, Monterey, CA, USA

Orcad V9.0 Schematics (Available on Request)

Source Code (Available on Request)

- MODEM

- QPSK (Quadrature Phase Shift Keying)

- 10MHz Data rate

- IF at 10MHz

- Upto 40MHz Data rate

- Reconfigurable Devices (FPGA)

- Digital Filtering

- Digital Modulation and Demodulation

- Applications: Point to Point W/Less Links and Satellite Communications.

- 32 bit RRC filtering

- IF at 10MHz

- Analog LPF with B/W 13MHz

- 10bit precision digital output

- Parallel multiplication (LUT based)

- When I carrier is sampled ‘1’ or ‘-1’, the Q carrier is sampled ‘0’ which means at any sampling instant we need to process only one of the carrier.

- PRBS Generator used to generate Random Sequence

- 10MHz IF, sampling rate = 40MHz

- 32 bit RRC Filter

- 16bit I,Q rail subfilters, clocked at 20MHz

- Automatic Gain Control

- Demodulation = De-Multiplexing and Inversion Control

- Timing Recovery

- Carrier Recover

- CMA Equalizer